【

儀表網 研發快訊】集成電路先進節點的晶體管接觸電阻隨器件持續微縮而急劇升高,已經成為摩爾定律物理極限的關鍵瓶頸。在摩爾定律驅動下,器件尺寸不斷微縮,與接觸面積成反比的晶體管源漏端接觸電阻急劇升高,在5nm工藝節點接觸電阻已經占整個晶體管電阻的38%,3nm工藝節點占比超過50%,2nm節點的占比會更高,接觸電阻已經成為先進工藝節點限制器件性能提升的關鍵瓶頸。

根據國際路線圖要求,2nm以下工藝節點必須把接觸電阻率降至10-9 ?·cm²。其核心挑戰在于金屬-半導體接觸界面存在很強的費米能級釘扎效應(Fermi Level Pinning, FLP),導致金屬的費米能級被釘扎在半導體價帶頂附近,肖特基勢壘高度幾乎不隨金屬功函數的改變而降低,從而引發巨大的本征接觸電阻。所有半導體中鍺擁有最強的費米能級釘扎效應,其釘扎因子S = 0.02,接近Bardeen極限S = 0。傳統觀點認為,處于半導體能隙中的金屬電子態滲透到半導體內部形成金屬誘生能隙態(MIGS),導致費米能級釘扎效應。由于金屬誘生能隙態密度反比于半導體帶隙寬度,所以帶隙越窄、MIGS密度越大、釘扎效應越強,因此,費米能級釘扎效應被認為是半導體材料的內稟屬性。

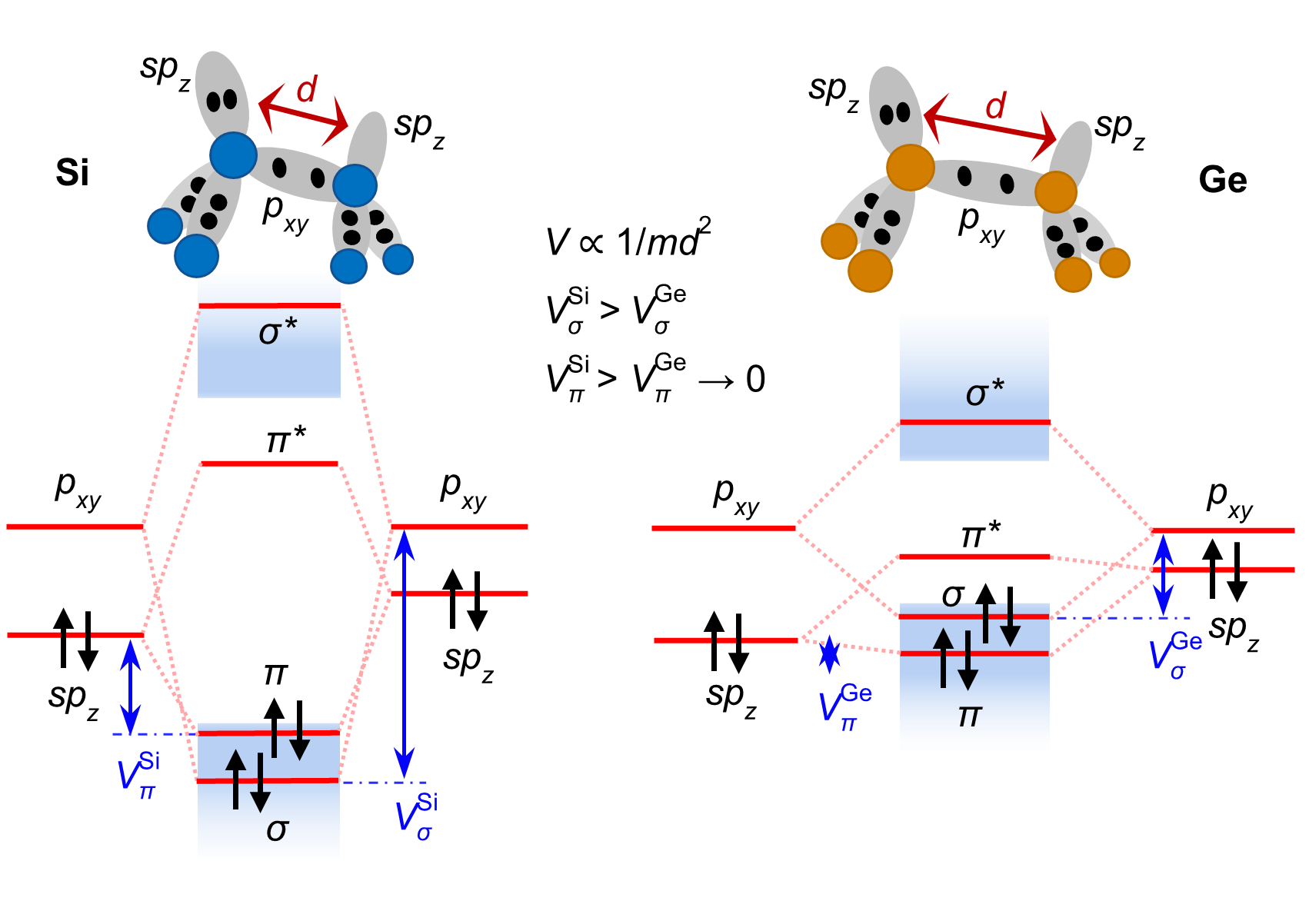

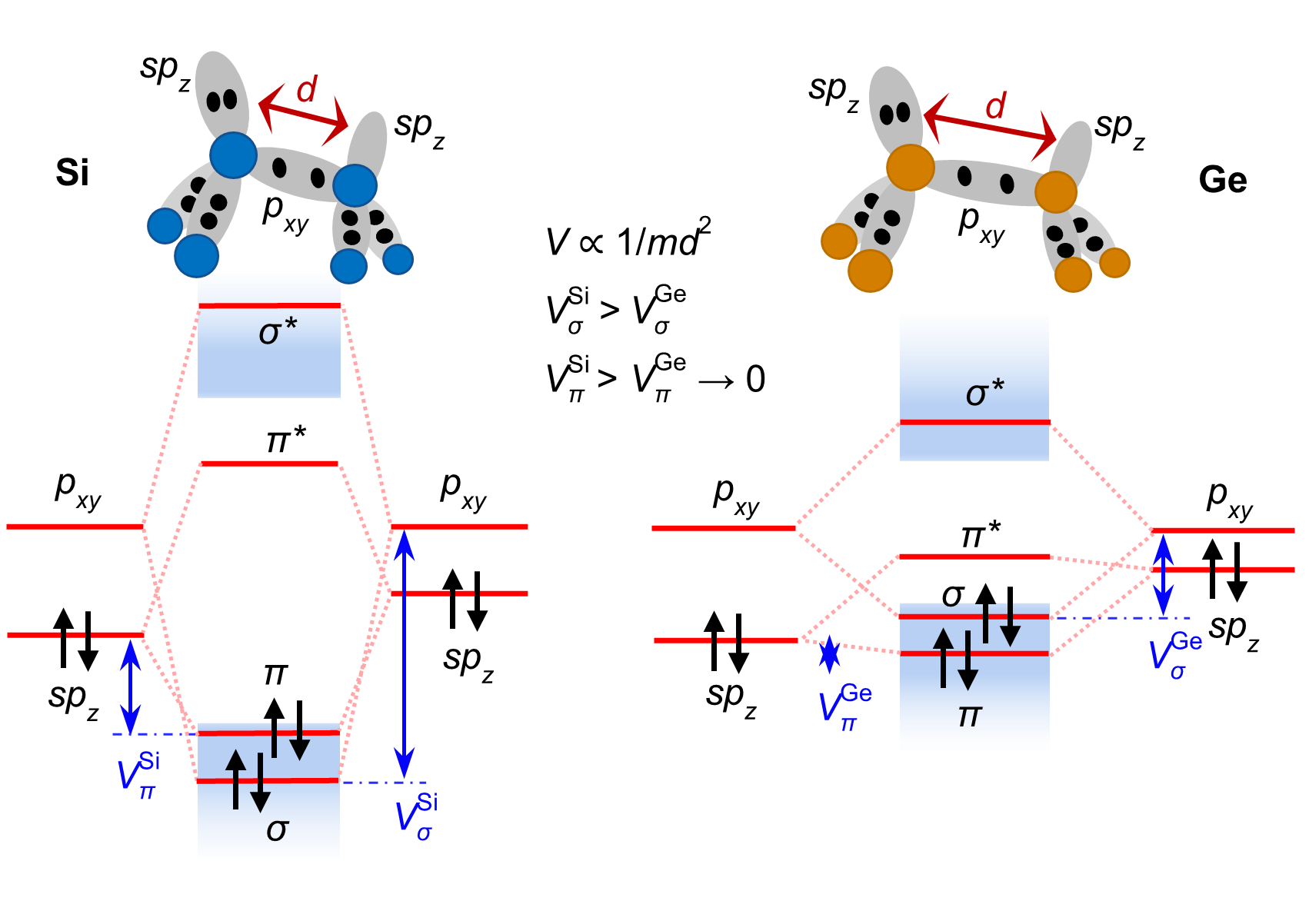

近期,中國科學院半導體研究所半導體芯片物理與技術全國重點實驗室李樹深院士和駱軍委研究員團隊使用第一性原理計算,揭示金屬-半導體接觸界面的費米能級釘扎效應存在新的物理機制。研究團隊發現,半導體懸鍵誘導的表面態對費米能級釘扎效應的貢獻至關重要,其影響甚至與金屬誘生能隙態MIGS相當。鍺擁有最強費米能級釘扎效應的關鍵在于鍺和硅傾向于形成不同的界面原子成鍵構型。半導體界面的懸鍵態在界面再構后形成新的成鍵態和反成鍵態,懸鍵上的電子完全占據新的成鍵態,從而降低系統能量,由于再構獲得的能量與鍵長平方成反比,從熱力學和動力學角度都使得硅傾向于保持穩定的自發面內成鍵構型(圖1),面內成鍵形成自鈍化效應,有效鈍化懸鍵降低了界面態密度,因此硅的費米能級釘扎效應較弱(釘扎因子S = 0.16)。而鍺的原子鍵長度比硅大4.3%,再構后獲得的能量很小,鍺傾向于保持非重構界面,直接和金屬成鍵后保留了更多的懸鍵和界面態,導致極強的費米能級釘扎效應(S = 0.02)。從鍺到硅再到金剛石,原子間距依次減小,界面懸鍵的自鈍化效應依次增強,界面懸鍵誘導表面態密度依次減小,導致費米能級釘扎效應依次降低。

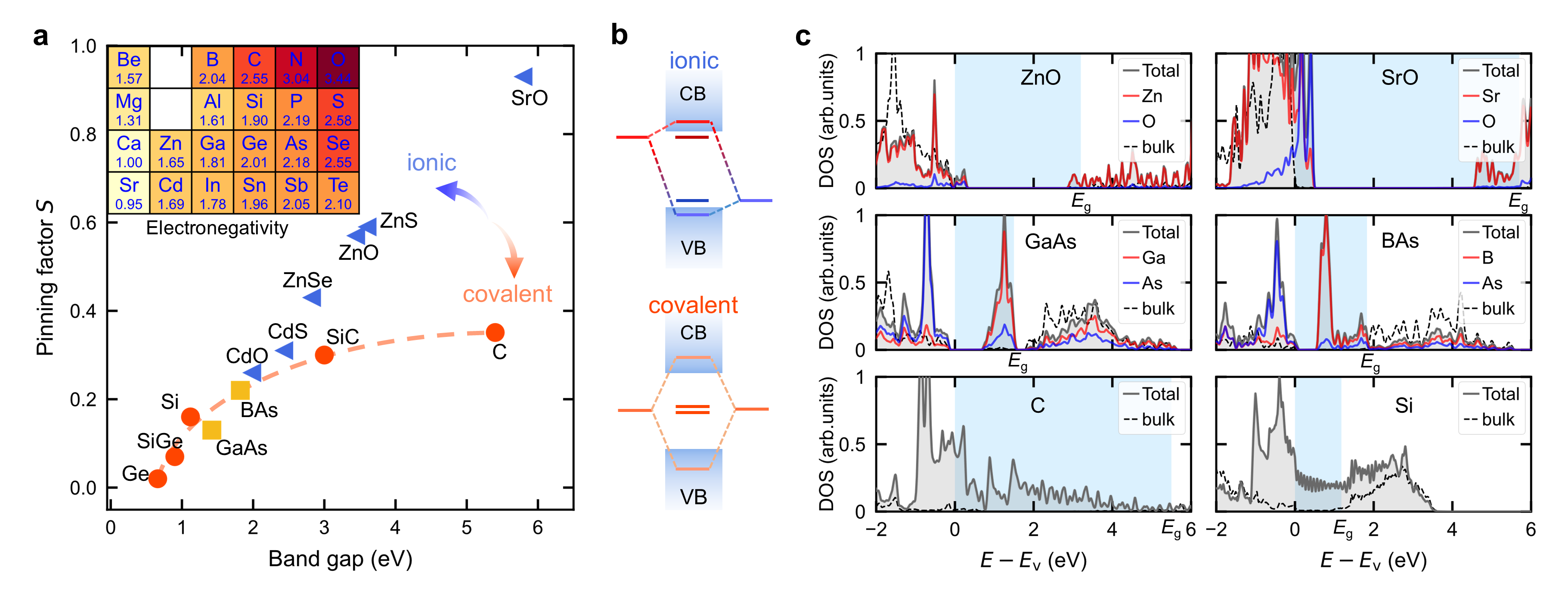

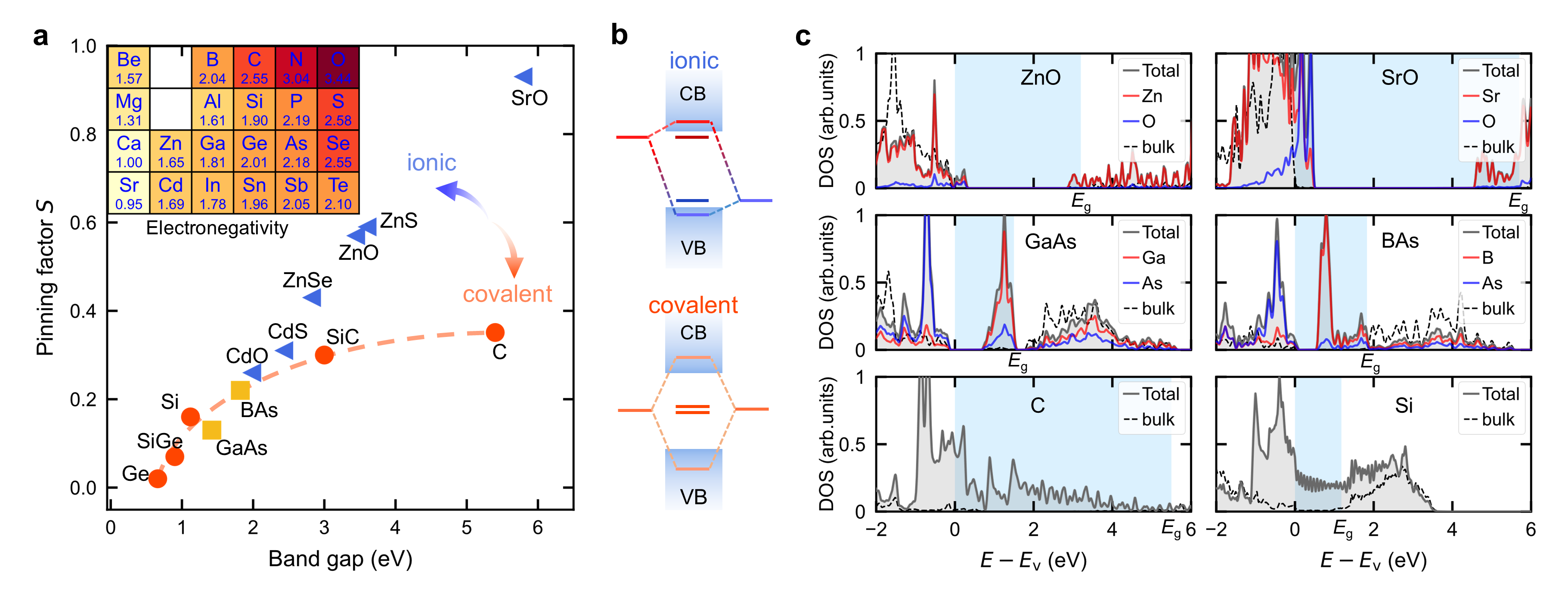

研究團隊進一步將該機理推廣至更廣泛的半導體體系,發現隨著半導體離子性增強,帶隙深處的懸鍵誘導表面態逐漸消失,費米能級釘扎顯著減弱(圖2)。由此建立起的“界面成鍵-懸掛鍵密度-釘扎強度”統一物理框架,為評估和預測不同材料體系的接觸特性提供了可靠的理論依據。

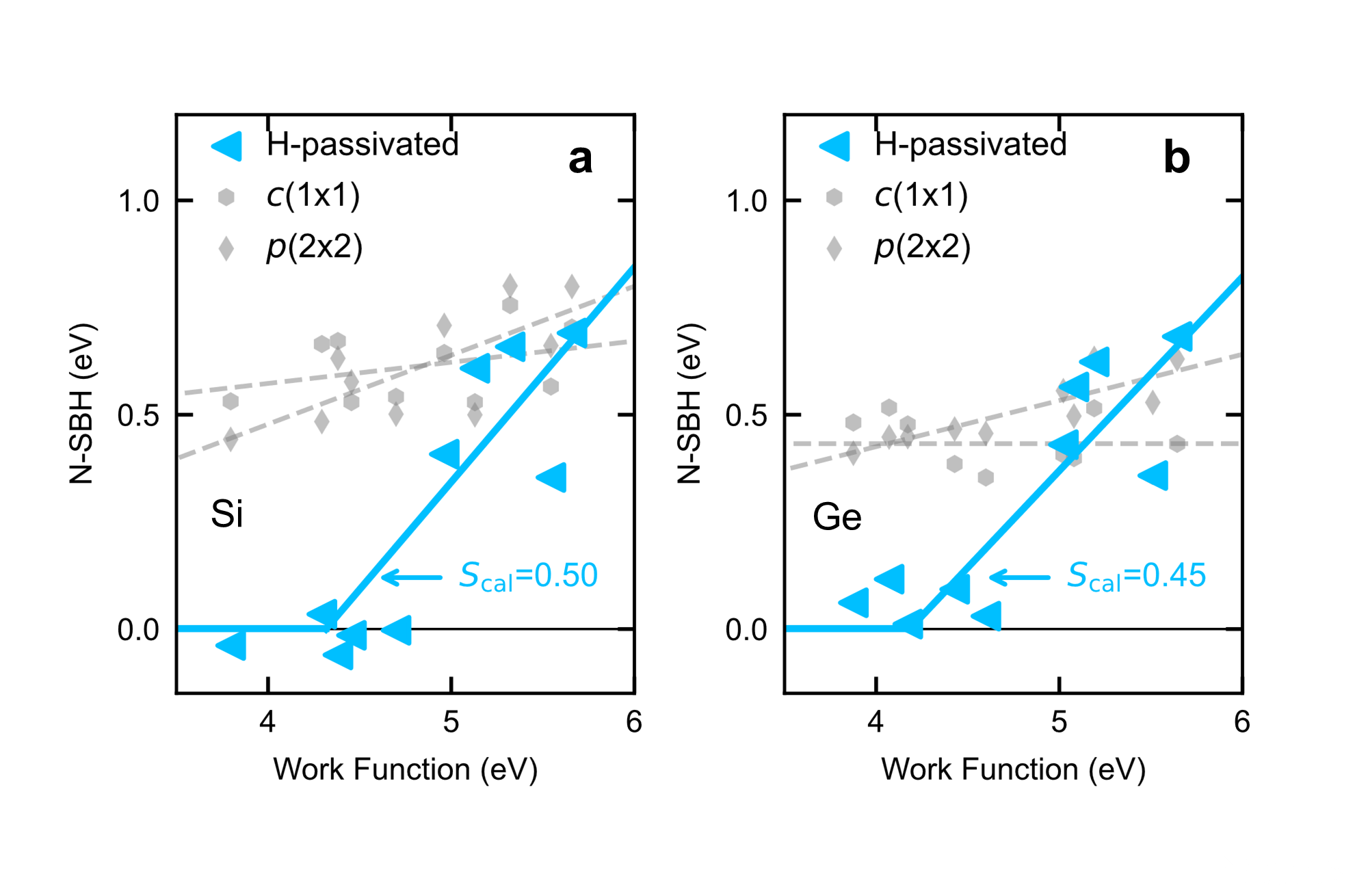

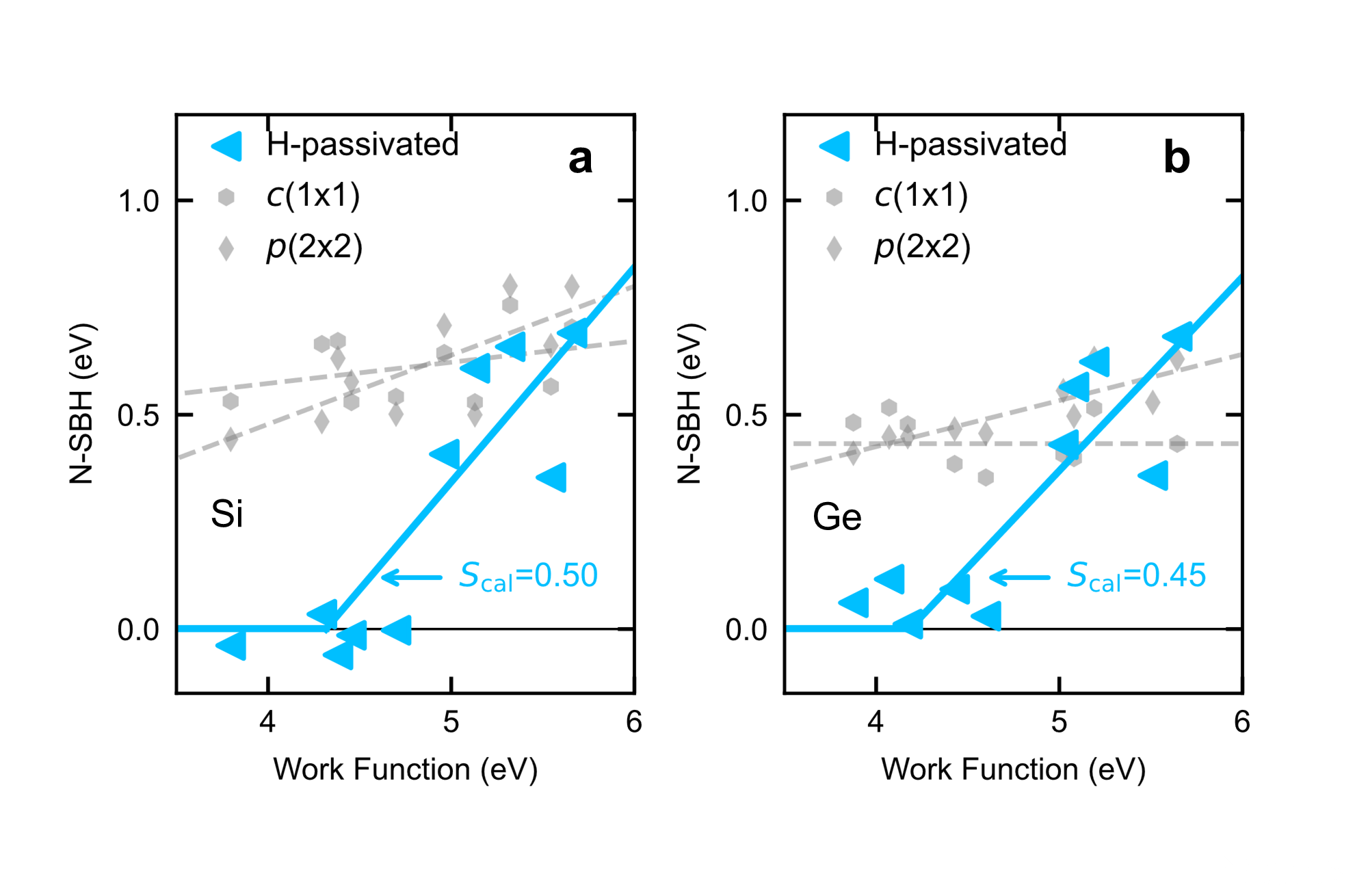

研究團隊從理論上進一步證明,可以通過引入外部非金屬原子來提高懸鍵的鈍化效果,從而大幅降低懸鍵誘導表面態密度。研究顯示使用氫原子可以完美鈍化硅和鍺界面懸鍵,達到消除所有懸鍵誘導表面態,從而大幅削弱費米能級釘扎效應,將硅和鍺的釘扎因子分別從0.16和0.02提升至?0.5和0.45(圖3),使得多種金屬可以將硅和鍺界面的肖特基勢壘降至接近理想的零值,為2nm以下工藝節點將接觸電阻率降至國際路線圖要求的10-9 ?·cm²提供了新思路。

該工作突破了傳統金屬誘生能隙態MIGS理論的局限,提出了通過調控界面原子成鍵構型來抑制FLP的新思路,為未來先進技術節點突破接觸電阻瓶頸提供了新思路。

該純理論的研究成果以“Self-passivation reduces the Fermi level pinning in the metal-semiconductor contacts”為題,11月27日發表在《自然·通訊》上。半導體芯片物理與技術全國重點實驗室主任駱軍委研究員為通訊作者,博士研究生向姿穎為第一作者。該研究得到了國家基金委青A延續項目(項目編號12525402 )和中國科學院穩定支持青年團隊(項目編號YSBR-026)的資助。

圖1:半導體界面的斷鍵產生高密度表面態導致強費米能級釘扎效應。通過面內成鍵的自鈍化效應有效鈍化懸鍵降低硅的費米能級釘扎效應。

圖2:半導體離子性-懸鍵誘導表面態-費米能級釘扎強度的內在規律。隨著離子性增強,帶隙深處的懸鍵誘導表面態密度顯著降低,釘扎隨之減弱;相反,共價性更強的半導體帶隙深處的懸鍵誘導表面態密度更高,即使帶隙寬度相近,也會表現出更強的釘扎。

圖3:通過使用氫原子可以完美鈍化硅和鍺界面懸鍵,消除所有懸鍵誘導表面態,從而大幅削弱費米能級釘扎效應,將硅和鍺的釘扎因子分別從0.16和0.02提升至?0.5和0.45。

所有評論僅代表網友意見,與本站立場無關。