【

儀表網 研發快訊】近日,集成電路學院(信息與電子工程學院)王國興教授課題組在面向無線通信應用的寬帶高精度

模數轉換器芯片領域取得了顯著進展,相關研究成果以“A 6.4-GS/s, 200-MHz BW 77.3-dB DR 71.5-dB SNDR 2× TI Extrapolated CT DSM Employing Broadband Hybrid-Inputs Adder and Nonlinearity-Suppression DAC Encoder”為題發表在國際頂級集成電路期刊IEEE Journal of Solid-State Circuits(JSSC)上。論文第一作者為集成電路學院(信息與電子工程學院)博士生劉悅凱,通訊作者為祁亮副教授,王國興教授為論文的共同作者。

研究背景

寬帶高精度模數

轉換器是移動應用通信和物聯網硬件中的核心電路模塊。其中,連續時間ΔΣ調制器(CT-DSM)因其阻性輸入阻抗和抗混疊濾波特性,在無線收發機領域得到了廣泛應用。然而,受限于自身的過采樣特性,CT-DSM芯片在大帶寬應用背景下需要工作在超高速采樣時鐘下,這極大地增加了芯片設計的難度,并限制了系統的能效。

研究內容

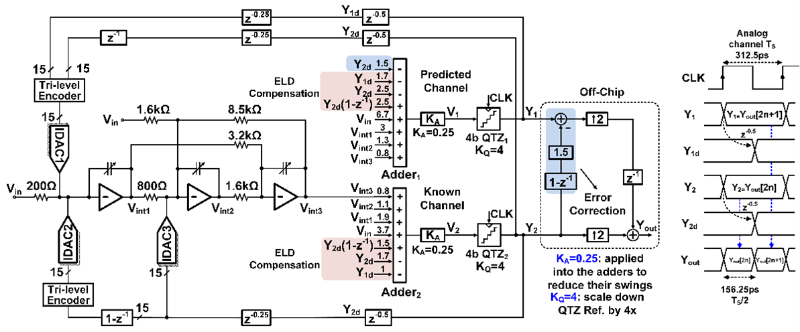

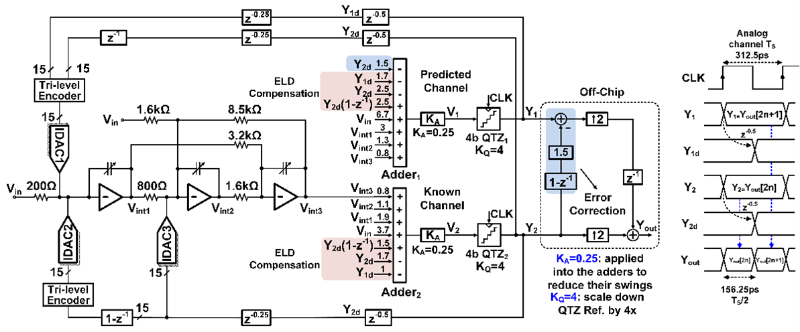

2× TI CT DSM模擬外插預測架構系統框圖

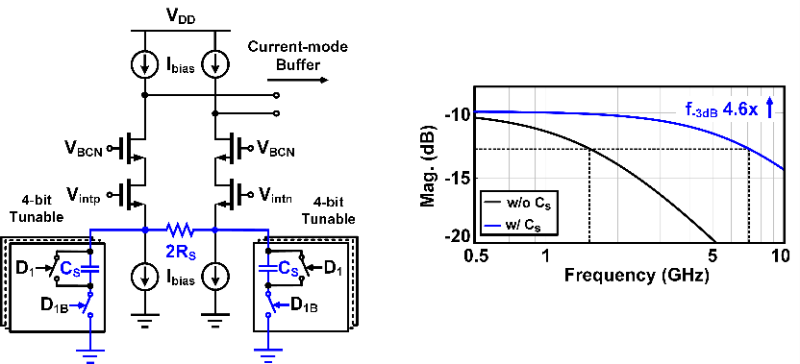

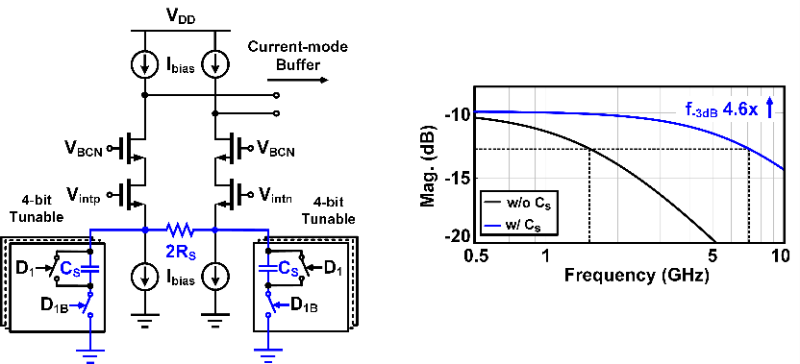

電容電阻并聯型源極退化跨導輸入前端電路圖及帶寬提升效果圖

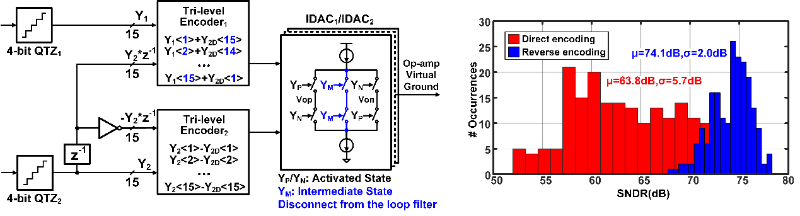

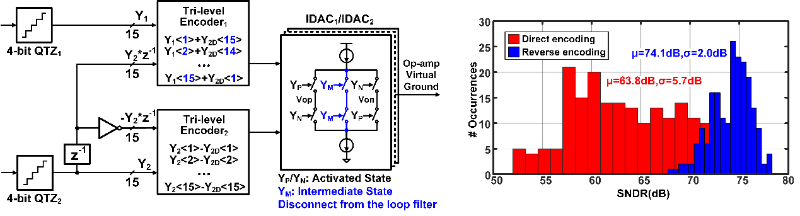

使用反向編碼的外環三態IDAC電路示意圖及性能提升效果圖

針對寬帶CT-DSM存在的過采樣率受限問題,研究團隊將時鐘交織技術(TI)應用到寬帶CT-DSM架構中,并基于模擬外插預測架構,采用了積分器級聯前饋式環路濾波器,在噪聲傳遞函數中實現了零點優化。在電路設計方面,研究團隊針對多路輸入的加法器電路模塊,提出了混合型輸入前端的電流型加法器,并創新性地設計了電容電阻并聯型源極退化跨導(Gm)輸入前端,顯著提高了跨導輸入路徑的帶寬。此外,針對外環DAC失配問題,研究團隊提出了針對三態IDAC的反向編碼方式,大幅降低了對外環DAC失配的敏感度。

研究成果

2× TI CT DSM芯片顯微照片和版圖布局圖

單音信號激勵下芯片輸出頻譜圖

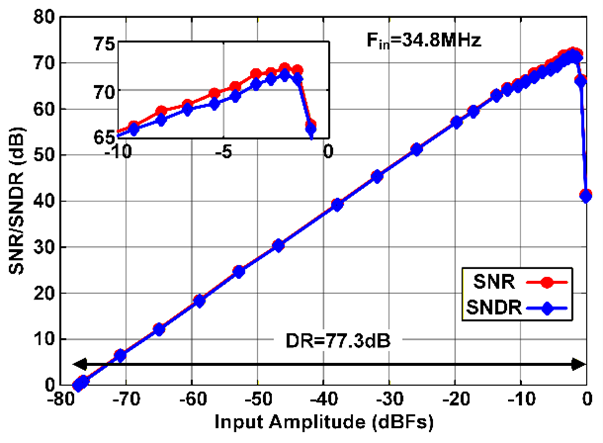

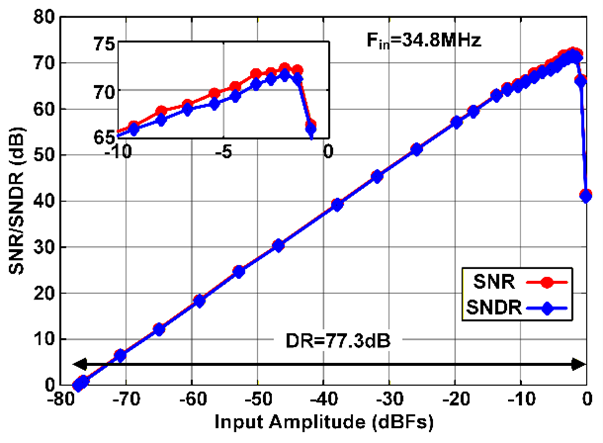

動態范圍測試結果圖

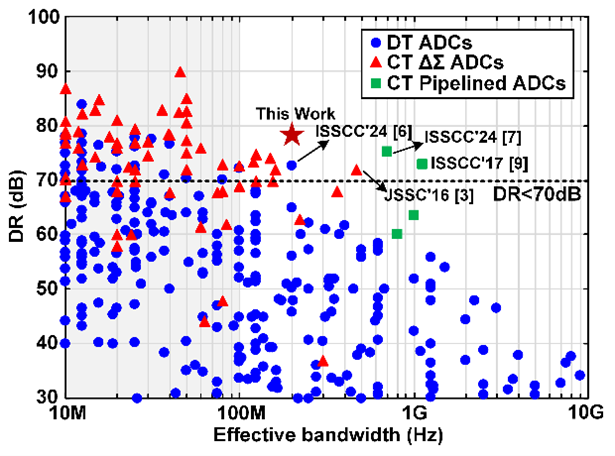

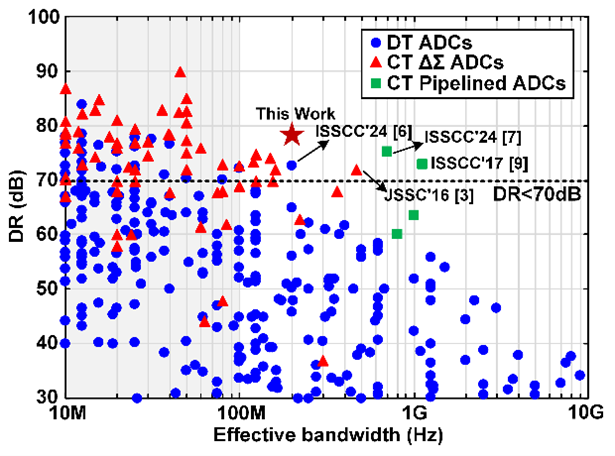

先進模數轉換器性能對比圖

該原型芯片采用28nm CMOS工藝制造,核心面積為0.13mm²,實現了71.5dB的SNDR和77.3dB的動態范圍(DR)。在目前已報道的帶寬不低于100MHz的先進寬帶模數轉換器芯片中,其動態范圍指標達到了國際領先水平。該研究成果為寬帶高精度ΔΣ型模數轉換器芯片的系統架構設計提供了新的解決方案。

所有評論僅代表網友意見,與本站立場無關。